嵌入式系统启动流程

这里说的 “三级引导” 并不是一个固定的、标准的术语,而是想强调,在某些系统里,bootloader 可以再拆得更细,例如。BootROM 不是严格意义上“只能从 ROM 启动操作系统” 的意思,而是指芯片上电复位后,第一段固定的启动程序,通常固化在 ROM(只读存储器)或 mask ROM、OTP ROM,甚至是 eFuse 或者内嵌 Flash 中。可以是单级的,也可以是多级分层的。对 Arm

1、基础概念

1.1 bootrom

BootROM 不是严格意义上“只能从 ROM 启动操作系统” 的意思,而是指芯片上电复位后,第一段固定的启动程序,通常固化在 ROM(只读存储器)或 mask ROM、OTP ROM,甚至是 eFuse 或者内嵌 Flash 中。

它的职责是:

- 初始化最基本的硬件环境(如时钟、SRAM、引脚模式)

- 决定启动介质(NAND、NOR、SPI Flash、SD 卡、USB、UART 等)

- 搬运/加载下一阶段的 bootloader 到片内 SRAM。

换句话说,BootROM 是 SoC 厂商写死的第一阶段代码,它并不等于“操作系统”,而是负责把后续代码拉起来。

广义上,ROM 可以指的存储器:

- 真·只读存储器(mask ROM,无法更改)

- eFuse/OTP(一次性可编程)

- 内嵌 Flash(有些 MCU/SoC 用它代替 mask ROM)。

在有些资料中,厂商也会把 BootROM + NAND/NOR 的启动扇区统称为“ROM”,这是习惯性说法。

1.2 bootloader

bootloader 本身就是一个广义的概念,它并不是指某一个特定的软件,而是指 “在操作系统启动之前运行的所有引导程序”。可以是单级的,也可以是多级分层的。

🔹多级引导的层次划分

不同的芯片/架构可能会分为多级:

- ROM Code / BootROM(第 0 级)

- 固化在 SoC 内部,不可修改

- 上电后 CPU 首先执行

- 职责:最小化初始化、选择启动介质、加载第一级 bootloader 到 SRAM

- 一级 bootloader(Stage 1 Bootloader / SPL,通常很小)

- 由开发者提供,存放在启动介质的最前面

- 通常运行在片内 SRAM(容量有限,比如 S3C2440 只有 4KB)

- 职责:初始化 DRAM、NAND 控制器,加载更大的二级 bootloader

- 二级 bootloader(Stage 2 Bootloader,例如 U-Boot)

- 存放在 NAND/NOR/SD 等存储器中,由一级 bootloader 搬运到 DRAM 后运行

- 功能完善:外设驱动、文件系统、网络下载、命令行、烧写功能、加载内核

- 三级引导(有些系统才有)

- 比如 U-Boot 本身可以分 SPL(小的前置程序)+ main U-Boot

- 或者在 PC 上的 BIOS/UEFI → boot sector → GRUB → OS

这里说的 “三级引导” 并不是一个固定的、标准的术语,而是想强调,在某些系统里,bootloader 可以再拆得更细,例如。严格来说,大家常用的叫法通常只有 BootROM → Stage 1 → Stage 2 → OS,但不同的社区/文档里命名方式会有点出入。

- 最终操作系统内核

- bootloader 的最后一步就是把内核搬到内存合适位置,并跳转到入口点执行

2、以 S3C2440 为例

S3C2440 的启动时读取的第一条指令是在内存 0x00 地址处(注意:对于S3C2440芯片设计为0x0,其他芯片不一定)。

上电后内存中没有数据,那么 0x00 地址处的指令如何放进去?

我们首先要了解一个基础知识:NAND FLASH 不可以直接运行程序,而 NOR FLASH 却可以(片上执行)。

- NAND FLASH 管脚复用,数据总线和地址总线复用。NOR FLASH 有地址总线和数据总线,可以直接连接到系统总线上、支持随机存取

- NAND Flash 支持页级别的随机访问,但不支持字节级别的随机访问。

- NOR Flash:支持字节级的随机访问,CPU 可以直接通过地址线读取任意一个字节并执行代码(即 XIP, Execute-In-Place)

- NAND Falsh 通常需要一个控制器去控制(例如很多 SOC 上的 NAND Flash 控制器)。而 NOR Flash 则不需要,它不需要单独的控制器去控制。

- NAND/NOR Flash 都可以通过 SPI 总线控制。有些是否为了节省成本,省去布线的麻烦,都用 SPI Flash。

2.1 NAND 启动

板卡出厂的时候,厂家会在 NAND FLASH 中固化相关启动镜像。

上电后,2440 硬件会自动从 Nand Flash 中读取 4K 到片内 RAM 上(SRAM),同时片内 RAM 上前 4K 被映射到[内存]的 0x0 地址处(映射的过程也是硬件的自动操作的过程)。CPU 从 0 地址上读取第一条指令(前4字节),执行…

- stage1:Reset 复位后,Nand Flash 控制器将 Nand 前 4K 代码复制到 SRAM 中运行(这部分代码可以理解为 SPL)

- stage2:这部分代码负责配置内存和 Flash,然后将 uboot 代码复制到内存(DDR)中,然后跳转到内存中运行(可以理解为 Uboot)

- stage3:最后 uboot 启动 Linux 内核(OS),然后内核去挂载根文件系统,进入命令行启动应用程序(可以理解为 OS)

2.2 NOR 启动

板卡出厂的时候,厂家会在 NOR FLASH 中固化相关启动镜像。

如果配置为 NOR FLASH 启动,0x00000000 就是 NOR FLASH 实际的起始地址,NOR FLASH 中的程序就从这里开始运行,不涉及到数据拷贝和地址映射。

- stage1:Reset 复位后,程序直接从 NorFlash 开始运行,初始化内存,将 uboot 拷贝到内存中

- stage2:跳转到内存中运行,然后启动内核。

3、ARM 架构中的安全启动

推荐先阅读:

ARM 学习笔记(一)

ARM 学习笔记(二)

3.1 TrustZone

🔹TrustZone 的起源

- 时间背景:

- 2003 年左右 ARM 推出 ARMv6K 架构时,已经有了最早的 TrustZone 技术雏形;

- 真正普及是在 ARMv7-A(Cortex-A 系列)开始,尤其是智能手机爆发时期(2005–2010)。

- 动机:在此之前,嵌入式系统大多数是单一用途(比如机顶盒、打印机),不太需要复杂的安全隔离。但随着手机、平板 等 开放应用平台 出现,情况变了:

- 手机要能安装第三方 APP;

- 手机要处理安全敏感任务(SIM 卡、支付、DRM、VPN、企业安全);

- 同一台设备要承载 “可信代码” 和 “不可信代码”。

这就迫使 ARM 提供一种硬件级别的隔离机制:让 CPU 在同一核心上也能划分出 安全世界 (Secure World) 和 普通世界 (Normal/Non-secure World)。

🔹为什么需要 TrustZone

- 软件隔离不够安全

- 单纯靠 OS 内核做隔离(用户态 vs 内核态)不足以抵御恶意软件

- Android/Linux 内核本身可能有漏洞,一旦被利用,安全功能就会被绕过。

- 可信执行环境 (TEE) 的需求

- 电信运营商要保护 SIM 卡相关的密钥;

- 内容提供商要保护 DRM;

- 金融厂商要保护支付/加密逻辑;

- 企业要保证设备管理和 VPN 通道可信。

👉 这些功能不能和普通 APP 跑在一起,需要有个小而可信的“安全小环境”

- 硬件生态统一

- 如果让每家厂商自己搞一套安全处理器,碎片化会严重。

- ARM 直接在 CPU 架构里内置一个“安全世界”支持,大家就能基于统一机制开发。

🔹 TrustZone 的设计核心

- 世界切换 (World switch):

- CPU 引入了 Secure/Non-secure 状态位 (NS bit)。

- 指令 smc (Secure Monitor Call) 用来在两个世界之间切换。

- 硬件隔离:

- 内存、外设都带有安全属性(比如 MMU + TrustZone Address Space Controller(TZASC))。

- 普通世界不能直接访问安全世界的资源。

- 安全监控器 (Secure Monitor):

- 相当于世界切换时的“中介”,运行在最高特权级,保证切换过程不会被篡改。

3.2 Trusted Firmware(ATF)

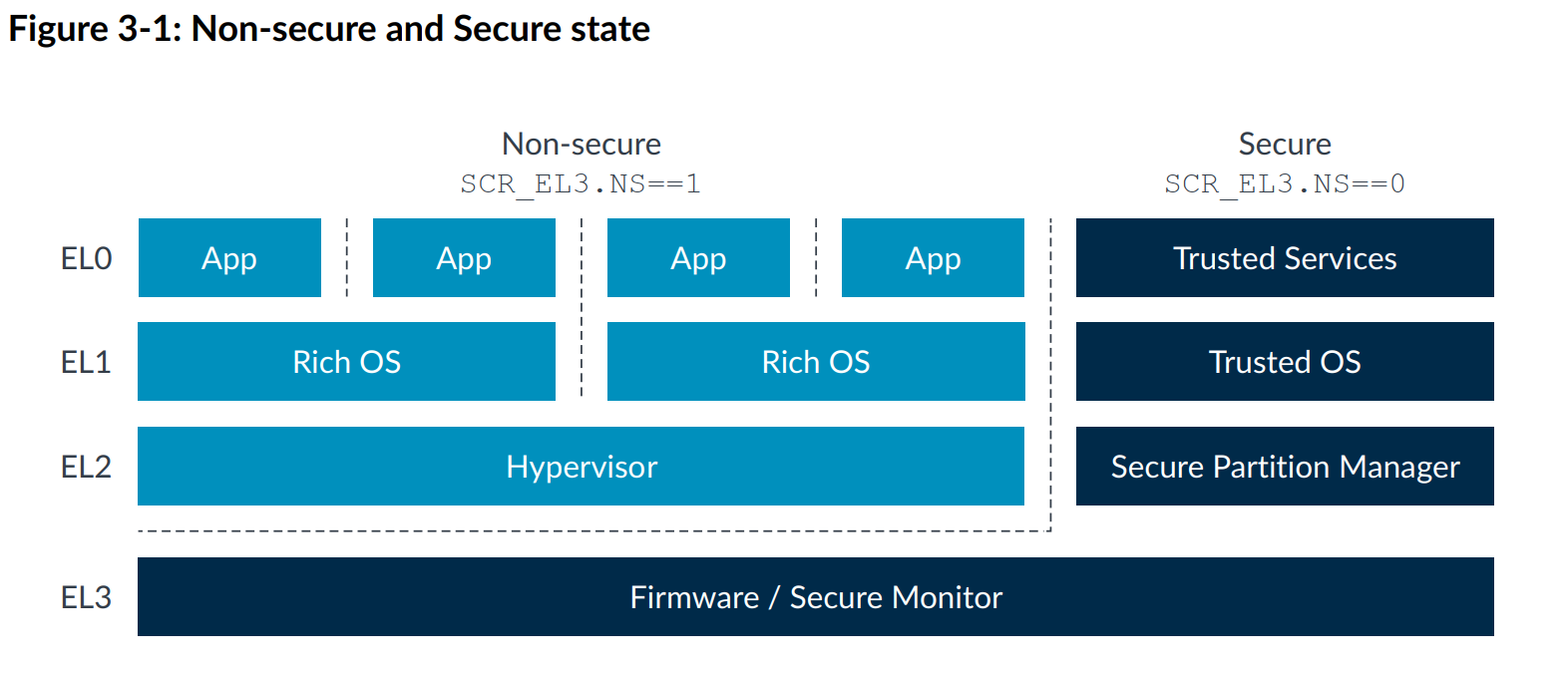

TF(Trusted Firmware)是 ARM 在 Armv8 引入的安全解决方案,为安全提供了整体解决方案。它包括启动和运行过程中的特权级划分,对 Armv7 中的 TrustZone(TZ)进行了提高,补充了启动过程信任链的传导,细化了运行过程的特权级区间。

处理器的执行特权等级基于异常级别(EL)划分:

- EL0(应用层级)可分为安全(Secure)与非安全(No-Secure)状态

- EL1(操作系统层级)可分为安全(Secure)与非安全(No-Secure)状态

- EL2(虚拟机监控器层级)在Armv7-A至Armv8.3-A架构中仅支持非安全状态。从Armv8.4-A架构开始,EL2可支持安全与非安全状态

- EL3(安全监控器层级)仅存在于安全域——安全与非安全状态间的软件驱动转换仅能在此层级实现

从高 EL 转低 EL 通过 ERET 指令,从低 EL 转高 EL 通过 exception,从而严格区分不同的特权级

ATF 相关源码可以学习:

https://github.com/ARM-software/arm-trusted-firmware

关于 ATF 启动这里先整个宏观的概念。这个 blog 讲的很好,就不重复写了,自己写还写不到这么清晰,图页很漂亮。

ARM Trusted Firmware分析——启动、PSCI、OP-TEE接口

这里直接贴图:

这里就直接上总结,总结下我个人觉得比较重要的东西。

- BL1 通常是 bootrom,运行在 EL3,初始化相关硬件,加载 BL2

- BL2 通常运行在 SRAM 中,运行在 EL1,初始化相关硬件(DRAM)

- BL2 会搬运 BL31、BL32、BL33 到 DRAM 中

- BL1、BL2 都是一次性的,系统启动后,不再起作用。系统运行期间,一直起作用的是 BL31、BL32、BL33

- BL31 比较重要,运行在 EL3,它通过 smc 指令为 Non-Secure World 持续提供涉及安全的服务。提供 PSCI 电源管理功能(例如 CPU 的使能)、安全非安全世界切换(World Switch)等

- 上述顺序启动过程中,都会包含数字签名等验证流程,确保镜像的安全性

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)