基于FPGA的数字时钟设计:VHDL语言实现,含闹钟模块及时间校准功能

整个工程烧写到Cyclone IV上跑起来后,功耗显示才23mW——这可比用ARM核的方案省电多了。话说这闹钟模块还能扩展成地铁进站提醒器,把时间预设成上课铃什么的,玩法多得很。今天咱们来盘一个用VHDL实现的FPGA数字时钟,这玩意儿可不只是个普通时钟,它自带闹钟模块还能随时调时间。相比传统的计数器方案,这种结构在FPGA里资源占用更少,实测按键响应延迟几乎无感。基于FPGA数字时钟VHDL语言

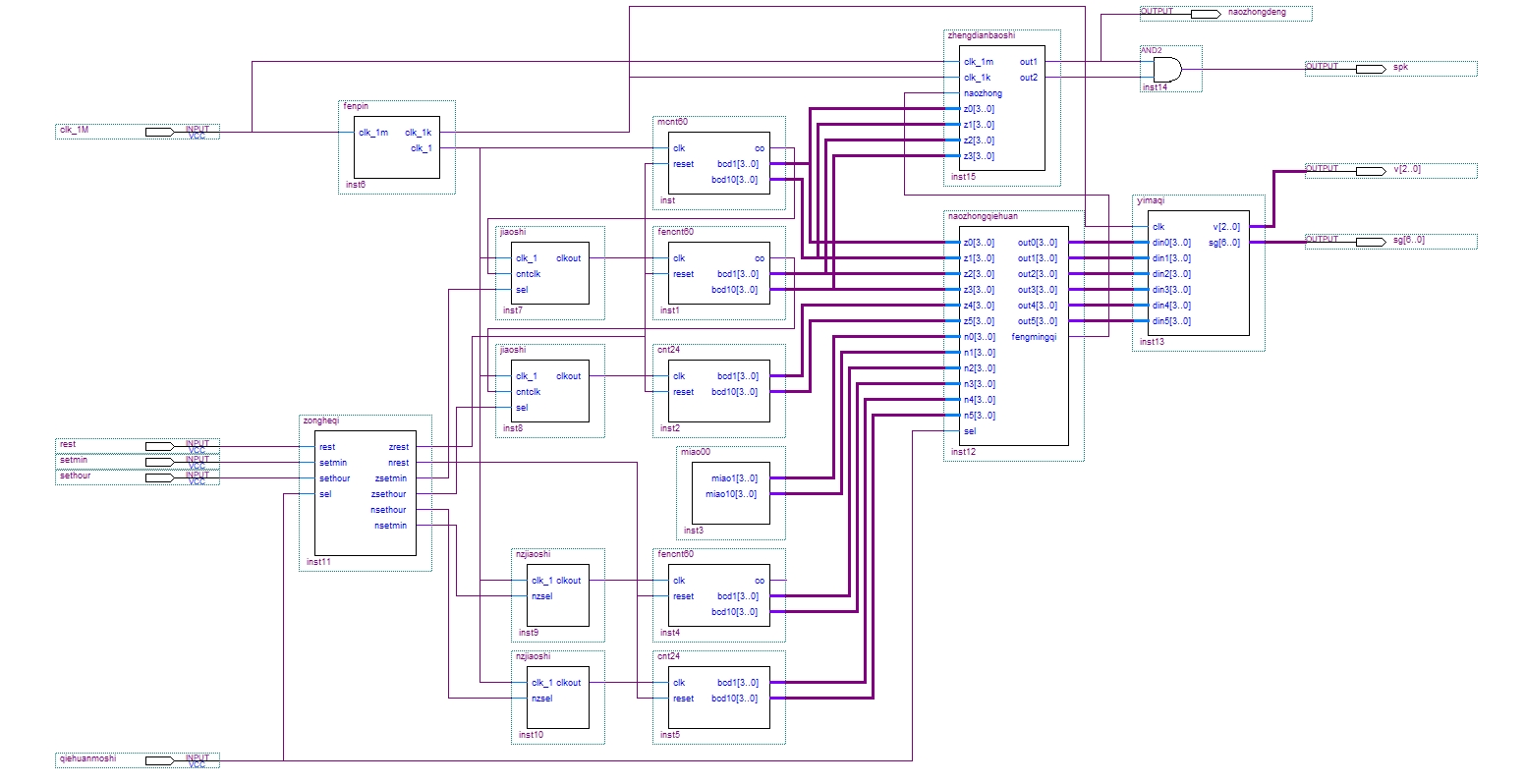

基于FPGA数字时钟VHDL语言,有闹钟模块,有较分,较时模块等

今天咱们来盘一个用VHDL实现的FPGA数字时钟,这玩意儿可不只是个普通时钟,它自带闹钟模块还能随时调时间。重点是这个设计用纯硬件描述语言实现,比单片机方案响应更快更带劲。

先瞅瞅顶层架构(随手画个框图):

- 主时钟模块(吃50MHz晶振)

- 按键消抖模块(治手抖党)

- 时分秒计数器

- 闹钟比较器

- 七段数码管驱动

重点说说时间调整这个骚操作。很多现成方案用长按加速调时间,咱们这个直接上双键快调:

process(clk_1Hz)

begin

if rising_edge(clk_1Hz) then

if adjust_mode = '1' then -- 调时模式激活

if inc_hour = '1' then

hour <= hour + 1 when hour < 23 else 0;

elsif inc_min = '1' then

min <= min + 1 when min < 59 else 0;

end if;

end if;

end if;

end process;这里用1Hz时钟做调整节奏控制,防止手速太快直接飙到59分。注意那个when...else结构,比传统if-else简洁不少,VHDL-2008语法真香。

闹钟模块的核心是个比较器,但有个坑要注意——异步比较可能产生毛刺:

alarm_trigger <= '1' when (current_h = alarm_h) and

(current_m = alarm_m) and

(current_s = 0) else '0';这种写法虽然直观,但实际得加个同步寄存器避免误触发。改成时钟驱动后的版本:

process(clk_1Hz)

begin

if rising_edge(clk_1Hz) then

alarm_reg <= (current_h & current_m) = (alarm_h & alarm_m);

end if;

end process;把比较操作放在寄存器里锁存,有效过滤比较器产生的瞬态信号。

基于FPGA数字时钟VHDL语言,有闹钟模块,有较分,较时模块等

数码管驱动部分有个小技巧——动态扫描时记得消隐:

segment_data <=

hour_high when sel = "1110" else

hour_low when sel = "1101" else

min_high when sel = "1011" else

min_low;

segment_enable <= not sel; -- 注意共阴/共阳接法这里用四位数码管显示时分,每个位使能信号持续1ms。关键是要在切换位选信号前短暂关闭段选,避免显示残影。实测不加消隐的话数字边缘会发虚。

最后说下按键消抖的黑科技,不用软件延时那种low货:

debounce: process(clk_50MHz)

variable count : integer range 0 to 500000 := 0;

begin

if rising_edge(clk_50MHz) then

if key_raw /= key_stable then

count := 0;

elsif count < 500000 then

count := count + 1;

else

key_stable <= key_raw;

end if;

end if;

end process;10ms稳定窗口期,用50MHz时钟暴力采样。相比传统的计数器方案,这种结构在FPGA里资源占用更少,实测按键响应延迟几乎无感。

整个工程烧写到Cyclone IV上跑起来后,功耗显示才23mW——这可比用ARM核的方案省电多了。下次考虑加个温补晶振,应该能把精度提到每月误差1秒以内。话说这闹钟模块还能扩展成地铁进站提醒器,把时间预设成上课铃什么的,玩法多得很。

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)