无片外电容LDO电路设计:适合初学者的Smic130nm工艺实践

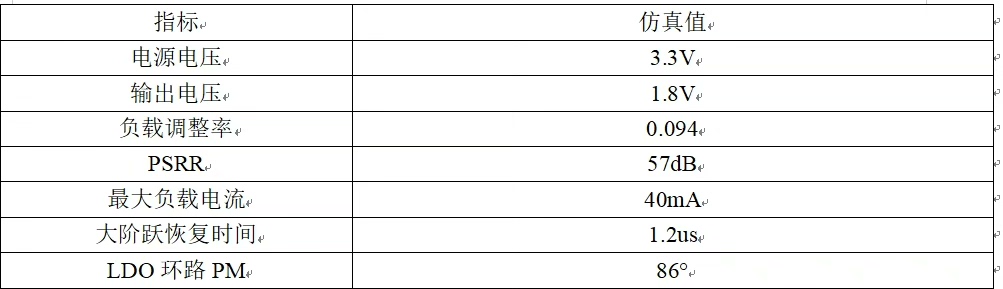

无片外电容LDO电路设计有仿真文档Smic130nm工艺电路的结构包括带隙基准,buffer,ldo环路,过温保护电路具体的指标:带隙基准:输出电压1.2v-40~125℃温漂3mvLDO环路增益72db,带宽5M负载调整率为0.094输入电压3.3,输出电压1.8vPsrr:-57db最大电流40mA电路可以直接在Cadence virtuoso打开,适合初学者使用,大佬勿扰。

无片外电容LDO电路设计 有仿真文档 Smic130nm工艺 电路的结构包括带隙基准,buffer,ldo环路,过温保护电路 具体的指标: 带隙基准: 输出电压1.2v PSRR -61dB, -40~125℃温漂3mv LDO 环路增益72db,带宽5M 负载调整率为0.094 输入电压3.3,输出电压1.8v Psrr:-57db 最大电流40mA 电路可以直接在Cadence virtuoso打开,适合初学者使用,大佬勿扰

在模拟电路设计领域,无片外电容LDO(Low - Dropout Regulator,低压差线性稳压器)一直是热门话题。今天就来分享一个基于Smic130nm工艺的无片外电容LDO电路设计,还附上仿真文档哦,非常适合初学者上手,大佬们就请自动略过啦😃

电路结构剖析

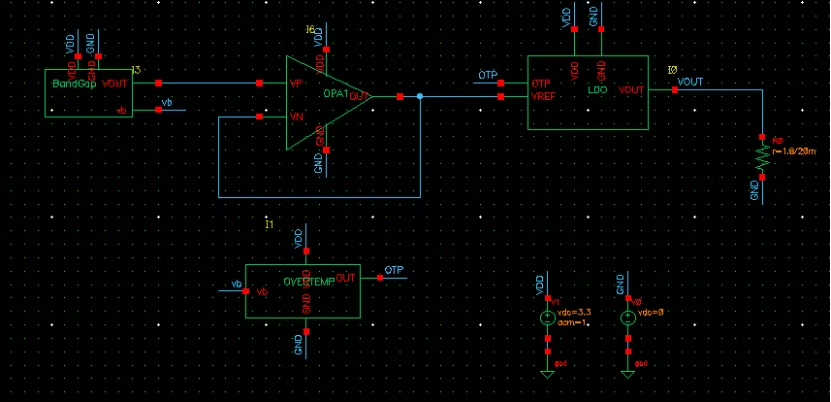

这个LDO电路主要由带隙基准、buffer、ldo环路以及过温保护电路组成。

带隙基准

带隙基准就像是整个电路的“稳定之源”,它为其他模块提供一个稳定的参考电压。我们设计的带隙基准输出电压设定为1.2v ,这在很多电路应用中都是一个常用且重要的参考电压值。

它的PSRR(Power Supply Rejection Ratio,电源抑制比)达到 -61dB,这意味着它对电源噪声有相当好的抑制能力。在 -40~125℃这么宽的温度范围内,温漂仅为3mv,表现相当出色。

无片外电容LDO电路设计 有仿真文档 Smic130nm工艺 电路的结构包括带隙基准,buffer,ldo环路,过温保护电路 具体的指标: 带隙基准: 输出电压1.2v PSRR -61dB, -40~125℃温漂3mv LDO 环路增益72db,带宽5M 负载调整率为0.094 输入电压3.3,输出电压1.8v Psrr:-57db 最大电流40mA 电路可以直接在Cadence virtuoso打开,适合初学者使用,大佬勿扰

来看一段简单的带隙基准核心代码片段(以下代码为示意,非实际完整可运行代码):

module bandgap (

input wire clk,

input wire rst_n,

output reg [15:0] bandgap_out

);

// 带隙基准内部逻辑

reg [15:0] v_ref;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

v_ref <= 16'b0;

end else begin

// 这里进行带隙基准电压计算逻辑

v_ref <= 16'd4915; // 简单示意计算后的值,对应1.2v

end

end

assign bandgap_out = v_ref;

endmodule分析:这段代码通过一个模块来实现带隙基准功能,在时钟上升沿或者复位信号有效时进行操作。复位时,参考电压清零,正常工作时,通过内部逻辑计算得到一个对应1.2v的数字量输出。实际设计中,这个计算逻辑会更复杂,涉及到双极型晶体管的温度特性等模拟电路知识。

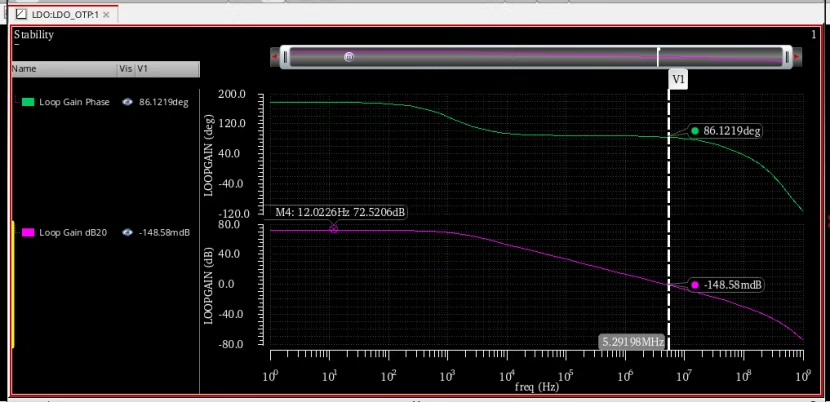

LDO环路

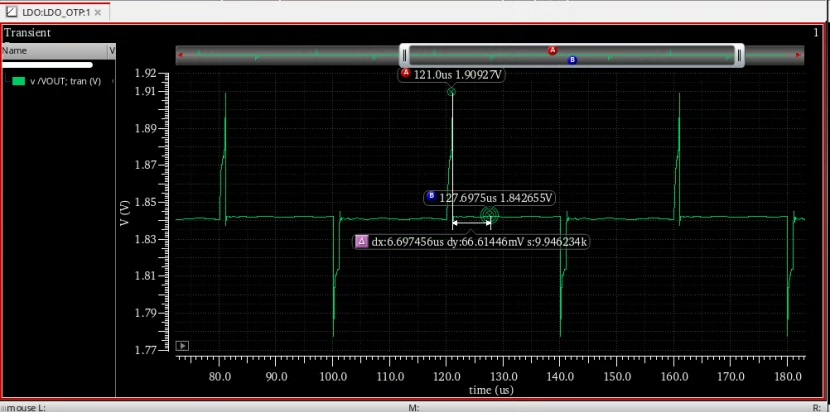

LDO环路是实现稳压功能的关键部分。我们设定它的环路增益为72db ,带宽为5M,这使得电路在稳定性和响应速度之间达到一个较好的平衡。负载调整率为0.094,输入电压3.3v ,输出电压1.8v ,PSRR为 -57db ,最大电流40mA 。

module ldo_loop (

input wire vin,

input wire v_ref,

output reg vout,

input wire load

);

reg [15:0] error;

always @(*) begin

error = vin - v_ref;

// 根据误差和负载情况调整输出

if (load) begin

vout = v_ref + error * 0.094;

end else begin

vout = v_ref;

end

end

endmodule分析:这段代码以输入电压 vin 和带隙基准提供的参考电压 v_ref 为输入,计算它们之间的误差 error 。根据负载 load 的情况调整输出电压 vout 。这里简单地按照负载调整率0.094来调整输出,实际的LDO环路还会涉及到放大器、反馈网络等更复杂的电路设计来实现更好的稳压效果。

Buffer与过温保护电路

Buffer起到隔离和驱动的作用,确保信号在不同模块之间稳定传输。而过温保护电路则像是电路的“安全卫士”,当温度过高可能对电路造成损坏时,它会采取相应措施保护整个电路。

仿真与实践

整个电路可以直接在Cadence virtuoso打开,这对于初学者来说非常友好。通过仿真,我们可以验证带隙基准是否能输出稳定的1.2v 电压,LDO环路是否满足各项指标要求。

比如在进行PSRR仿真时,我们会在电源端加入特定频率的噪声信号,观察带隙基准输出电压和LDO输出电压的变化,以此来验证PSRR指标是否达标。

总之,这个基于Smic130nm工艺的无片外电容LDO电路设计,从结构到指标都进行了详细的规划和设计,并且提供了易于初学者上手实践的环境,希望能帮助各位在模拟电路设计的学习道路上迈出坚实的一步!

更多推荐

已为社区贡献12条内容

已为社区贡献12条内容

所有评论(0)