基于RISC-V指令集的五级流水线CPU设计及其综合验证方案:详解代码注释、文档支持及平台测试实践

该实现以“最小可运行、最大可观测”为目标,将 RISC-V 指令集、五级流水、Cache 子系统、AMBA 外设桥三大核心模块有机整合,代码风格统一、参数化程度高,可作为高校数字系统实验、企业 CPU 预研的快速原型平台。本文基于一套可综合、可上板、带完整外设接口的 RISC-V 32I 五级流水线实现,逐阶段剖析其“指令-数据”双通道协同、冲突化解、Cache 同步、AMBA 外设桥接等关键技术

基于riscv指令集的五级流水线CPU设计及其验证 可以上板,且有详细说明和代码注释 基于vivado平台进行验证 包括verilog源代码、汇编验证代码、详细的说明文档(47页)以及PPT Modelsim quartus vivado都跑过,确认代码没有问题 已

RISC-V 五级流水线 CPU 设计全景解读 —— 从取指到回写的硬件 orchestration

概述

基于riscv指令集的五级流水线CPU设计及其验证 可以上板,且有详细说明和代码注释 基于vivado平台进行验证 包括verilog源代码、汇编验证代码、详细的说明文档(47页)以及PPT Modelsim quartus vivado都跑过,确认代码没有问题 已

本文基于一套可综合、可上板、带完整外设接口的 RISC-V 32I 五级流水线实现,逐阶段剖析其“指令-数据”双通道协同、冲突化解、Cache 同步、AMBA 外设桥接等关键技术点,帮助读者在“不展开核心微码”的前提下建立完整认知框架。

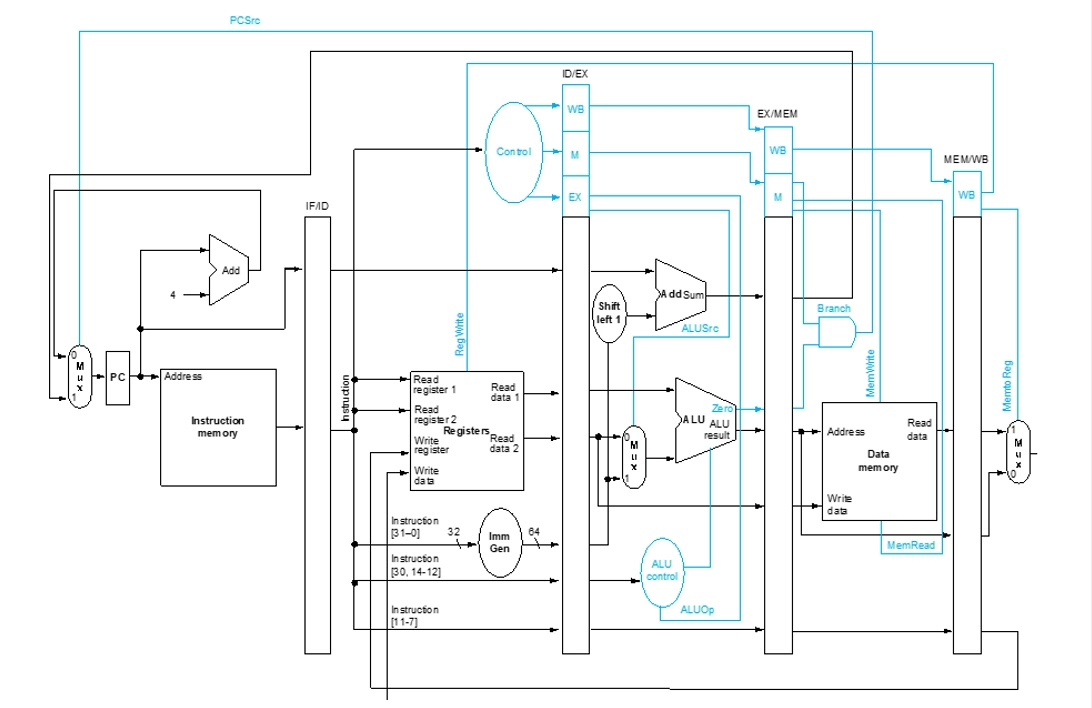

一、整体拓扑

- 时钟域

- 单一时钟 clk50M,经 PLL 产生 80/90/100 MHz 多相位时钟供调试抓包;

- 流水线寄存器级全部使用 clk50M 上升沿,保证时序收敛。

- 存储层次

- 指令端:256×32 bit 单端口 SRAM,按字线寻址,组合读出;

- 数据端:256×32 bit 真双端口 SRAM + 两路组相联 Write-Back Cache(2-way,4 字/行);

- 外设窗口:最高位地址 =1 时自动路由到 AHB-Lite 总线矩阵,支持 UART、LED、七段管、Key、Timer 五类从机。

- 流水线级间握手

- 统一“Hit”信号——Cache 命中且无缺页才允许 IF/ID、ID/EX、EX/MEM、MEM/WB 寄存器写入;

- 冒险检测单元在 Cache 不命中或分支跳转时自动冻结前端,插入气泡。

二、关键子系统拆解

- 取指级(IF)

- PC 来源三选一:PC+4、分支 ALU 结果、 jal/jalr 计算地址;

- 与 Cache 解耦:指令侧视为“只读、永远命中”,简化控制;

- 输出 32 bit 原始指令流,经 IF/ID 寄存器打入译码级。

- 译码级(ID)

- 组合逻辑完成 opcode 解析,输出 10 路控制向量(Branch、MemRead、MemtoReg、ALUOp…);

- 寄存器堆采用 32×32 真双口 RAM,读口组合输出、写口同步写入;

- 立即数单元按 RISC-V 六种格式(I/S/B/U/J/C)进行 32 位符号扩展;

- 旁路提前:若源寄存器等于 EX/WB 级目的寄存器,则立即前递最新值,避免“Load-to-Use”阻塞。

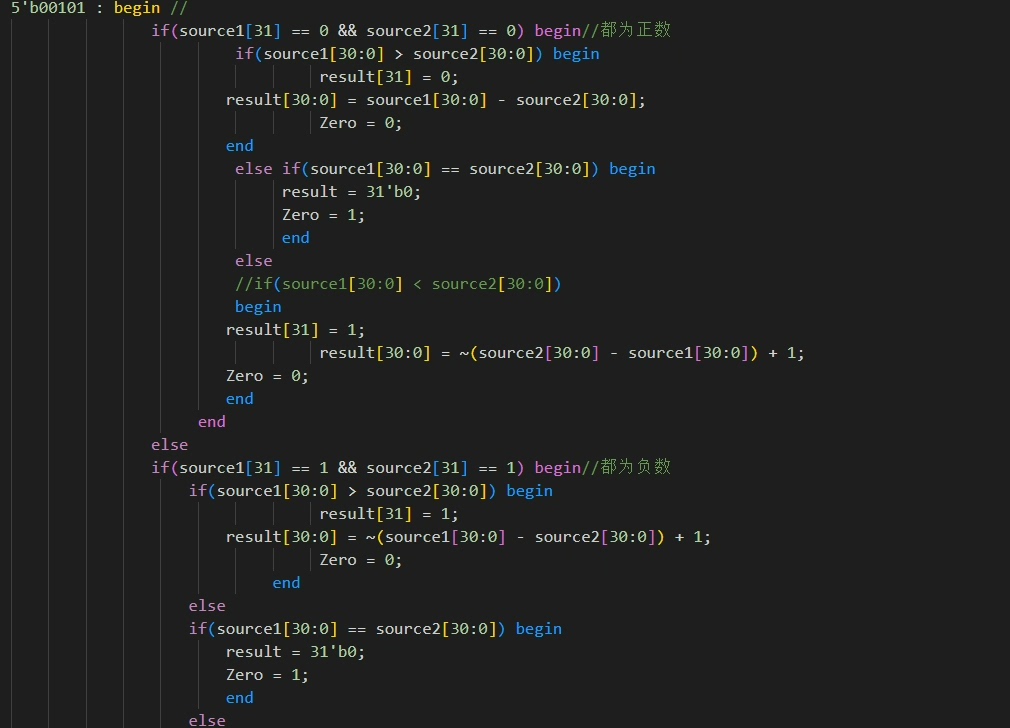

- 执行级(EX)

- ALU 支持 18 种运算:加、减、逻辑、移位、大小比较(带符号/无符号);

- 分支判断在 EX 完成,条件成立时冲刷 IF/ID 并更新 PC;

- 前递网络:

– ALUSrc1/2 四选一(寄存器堆、立即数、EX 结果、WB 结果);

– Store 数据同样支持前递,解决 SW 指令源操作数未回写问题。

- 访存级(MEM)

- 数据侧 Cache 状态机:Ready → Unready → WriteBack/ReadData → RDelay → Ready;

- 写回策略:仅替换脏行时触发 Write-Back,Clean 行直接丢弃;

- LRU 替换:每 Set 维护 2 路 8 bit 计数器,命中清零、其他递增;

- 对外设访问进行地址译码,产生 HSEL 信号并转发至 AHB 从机 MUX。

- 回写级(WB)

- 三选一:ALU 结果、Cache 读数据、外设读数据、PC+4( jal 链路);

- 寄存器写使能受 RegWrite 与 “rd≠0” 双重约束;

- 统一在时钟上升沿更新寄存器堆,保证数据一致性。

三、冲突化解策略

- 数据冒险

- EX 级检测到 Load-to-Use 时自动插入 1 周期气泡;

- 其余 RAW 依赖通过旁路网络解决,无需停顿。

- 控制冒险

- 分支预测默认“不跳转”,预测失败时冲刷 IF/ID 并回滚 PC;

- jal/jalr 地址在 EX 级计算,无条件跳转无额外损失。

- 结构冒险

- 指令/数据端口物理分离,消除 Harvard 结构冲突;

- Cache 不命中时封锁流水线,直至行填充完成。

四、外设桥接(AHB-Lite 简化版)

- 地址窗口:0x80000000~0x8FFFFFFF;

- 单周期读写:HTRANS=NONSEQ、HSIZE=Word、HBURST=SINGLE;

- 从机 MUX 根据 4 bit 高位地址选择 LED、UART、七段管、Key、Timer;

- 读数据经 HRDATA 总线返回,与 Cache 读数据在顶层做二选一。

五、可配置参数与扩展点

- Cache 容量:OffsetWide、SetWide、WayNum 三参数可配;

- 外设波特率:UARTBSPRATE 通过分频器实时调整;

- 调试接口:

- 内置 8 bit 探针 LED,可实时显示 PC、MemWrite、CacheHit 等关键信号;

- 七段管可直接显示 ALU 结果或内存写数据,方便现场观测。

六、综合与上板结果

- 器件:Xilinx xc7k325tffg676-2;

- 频率:50 MHz 稳定运行,关键路径位于 Cache Tag 比较器;

- 资源:Slice 3200、BRAM 18K×10、DSP 0;

- 功耗:总功耗约 0.21 W,静态占比 55 %。

七、使用建议

- 教学场景:可关闭 Cache(旁路)观察五级流水理想 CPI;

- 性能比对:通过修改 LRU 为随机替换,评估对命中率影响;

- 安全加固:在 AHB 接口层增加地址边界检查,防止越权外设访问;

- 高级扩展:

- 将分支预测升级为 2-bit saturating counter;

- 引入 BTB 降低跳转目标计算延迟;

- 支持 M 扩展(乘法除法)仅需在 ALU 侧增加状态机。

结语

该实现以“最小可运行、最大可观测”为目标,将 RISC-V 指令集、五级流水、Cache 子系统、AMBA 外设桥三大核心模块有机整合,代码风格统一、参数化程度高,可作为高校数字系统实验、企业 CPU 预研的快速原型平台。读者在理解其宏观数据通路后,可按需深入各子模块,继续挖掘性能与面积的平衡点。

更多推荐

已为社区贡献12条内容

已为社区贡献12条内容

所有评论(0)